68000 Conditions and the Condition Code Register

The computational power of all computers lies in their ability to choose between two or more courses of actions on the basis of the available information. Without such powers of decision, the computer would be almost entirely worthless, as it could only execute a long list of instructions “blindly”.

Instructions that make decisions at the assembly language level are used to implement constructs like IF…THEN…ELSE and REPEAT…UNTIL at the high-level language level. We are now going to look at the family of instructions that enable the programmer to synthesise high-level control constructs.

Learning Outcomes:

On completion of this lecture, you will be able to:

9.1 68000 conditions

There are instructions that only have an effect if a particular condition holds true. In the 68000, conditions are:

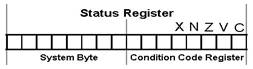

Fig. 9.1 Conditions the 68000 recognises

A computer chooses between two courses of action by examining the state of one or more bits in its CCR and associating one action with the outcome of the test and another action with the other outcome.

Remember that the Condition Code register (CCR) is a special register of the CPU. It contains a set of flag bits (X, N, Z, V and C) which are set or clear according to the result of an arithmetic or logical operation. That is, the CCR provides a status report about the operation.

Many instructions have an effect on the X, N, Z, V and C bits of the CCR. In the Instruction Set Summary:

* means the bit is affected ‘as you might expect’ --

– means the bit is unaffected -- it retains its present value

What you might expect…

Some instructions have no effect apart from their effect on the CCR: TST, CMP, BTST, etc…

The purpose of these instructions is to calculate an appropriate condition and place it in the CCR so that it can have a desired effect on program execution.

e.g.:

CMP.L D0,D1 evaluates [D1(0:31)] – [D0(0:31)]

CMP.B TEMP1,D3 evaluates [D3(0:7)] – [(TEMP1)]

CMP.L TEMP1,D3 evaluates [D3(0:31)] – [(TEMP1)]

CMP.W (A3),D2 evaluates [D2(0:15)] – [M([A3))]

The 68000 provides a family of four instructions that act on a single bit of an operand, rather than the entire operand: BTST, BSET, BCLR, BCHG. The selected bit is first tested to determine whether it is a one or a zero, and then it is operated on according to the actual instruction. In each of the bit manipulation instructions, the complement of the selected bit is moved to the Z-bit of the CCR and then the bit is left unchanged, set, cleared or complemented. The N-,V-,C- and X-bits are not affected.

9.5 Branch Conditionally

The 68000 provides the programmer with a toolkit containing instructions for the implementation of conditional structures:

Bcc <label> Branch to label on condition cc true.

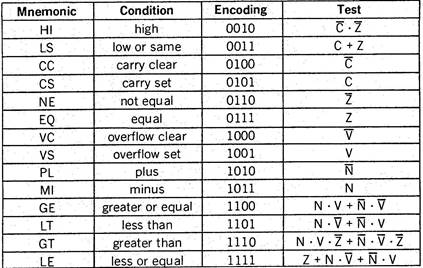

The condition cc, calculated into the CCR, is any one of the fourteen conditions listed below:

Fig. 9.2 authorised conditions with the Bcc instruction

After an arithmetic or logical operation is carried out, the value of the Z, N, C, V flags in the CCR are updated accordingly. These flag bits are used to determine whether the appropriate logical condition is true or false. For example, BCS LABEL causes the state of the carry-bit to be tested. If it is set, a branch is made to the point in the program called LABEL. Otherwise, the instruction immediately following BCS LABEL is executed.

We can divide branch instructions into two classes: those that branch on an unsigned condition and those that branch on a signed condition. Branch instructions used in conjunction with signed arithmetic are: BGE (Branch on Greater than or Equal), BGT (Branch on Greater than), BLE (Branch on Less than or Equal), and BLT (Branch on Less than). Branch instructions used in conjunction with unsigned arithmetic are: BHI (Branch on Higher than), BCC (Branch on Carry Clear), BLS (Branch on Less than or same), and BCS (Branch on Carry Set). Some assemblers let you write BHS (Branch on Higher or Same) instead of BCC, and BLO (Branch on Lower or Same) rather than BCS.

E.g: if [D0]=$CO and we perform the operation CMP.B #$2,D0, the result is C016-2516=9B16, and Z=0, N=1, V=0, C=0. If we perform a BHS, the branch will be taken because $CO is higher than $25 when using unsigned arithmetic. If we use a signed branch, BGE, the branch will not be taken, because $CO is less than $25 (i.e., -64 is less than 37).

9.6 Test Condition, Decrement and Branch Conditionally

The DBcc instruction makes it easier to execute a loop a given number of times. The assembly language form is:

DBcc Dn,<label> test condition cc, decrement Dn and branch to label if cc is false

Dn is a data register and <label> is a label used to specify a branch address. The label is assembled to a 16-bit signed displacement which permits a range of 32K bytes.

If the result of the test is true, the branch is not taken and the next instruction in sequence is executed (i.e., exit the loop).

If the specified condition is not true, the low-order 16-bits of register Dn are decremented by 1. In addition, if the resulting contents of Dn are equal to -1, the next instruction in sequence is executed.

Note that DBcc has the opposite effect to a Bcc instruction; a Bcc instruction takes the branch on condition cc true, whereas a DBcc instruction exits the branch on condition cc true.

As in the case of of the Bcc instruction, there are 14 possible computed values of condition cc, plus two static values: cc=T (true) and cc=F (false), as shown in Fig.10.1.

e.g.: DBF Dn,<label> always causes Dn to be decremented and a branch made to <label> until the contents of Dn are -1. Many assemblers permit the use of the mnemonic DBRA instead of DBF.

REFERENCES

Source: http://www.mee.tcd.ie/~assambc/3d1_l09n.doc

Web site to visit: http://www.mee.tcd.ie

Author of the text: indicated on the source document of the above text

If you are the author of the text above and you not agree to share your knowledge for teaching, research, scholarship (for fair use as indicated in the United States copyrigh low) please send us an e-mail and we will remove your text quickly. Fair use is a limitation and exception to the exclusive right granted by copyright law to the author of a creative work. In United States copyright law, fair use is a doctrine that permits limited use of copyrighted material without acquiring permission from the rights holders. Examples of fair use include commentary, search engines, criticism, news reporting, research, teaching, library archiving and scholarship. It provides for the legal, unlicensed citation or incorporation of copyrighted material in another author's work under a four-factor balancing test. (source: http://en.wikipedia.org/wiki/Fair_use)

The information of medicine and health contained in the site are of a general nature and purpose which is purely informative and for this reason may not replace in any case, the council of a doctor or a qualified entity legally to the profession.

The texts are the property of their respective authors and we thank them for giving us the opportunity to share for free to students, teachers and users of the Web their texts will used only for illustrative educational and scientific purposes only.

All the information in our site are given for nonprofit educational purposes